Semiconductor Divisioun Samsung Foundry huet ugekënnegt datt et d'Produktioun vun 3nm Chips an hirer Fabrik zu Hwasong ugefaang huet. Am Géigesaz zu der viregter Generatioun, déi FinFet Technologie benotzt huet, benotzt de koreanesche Ris elo GAA (Gate-All-Around) Transistorarchitektur, wat d'Energieeffizienz wesentlech erhéicht.

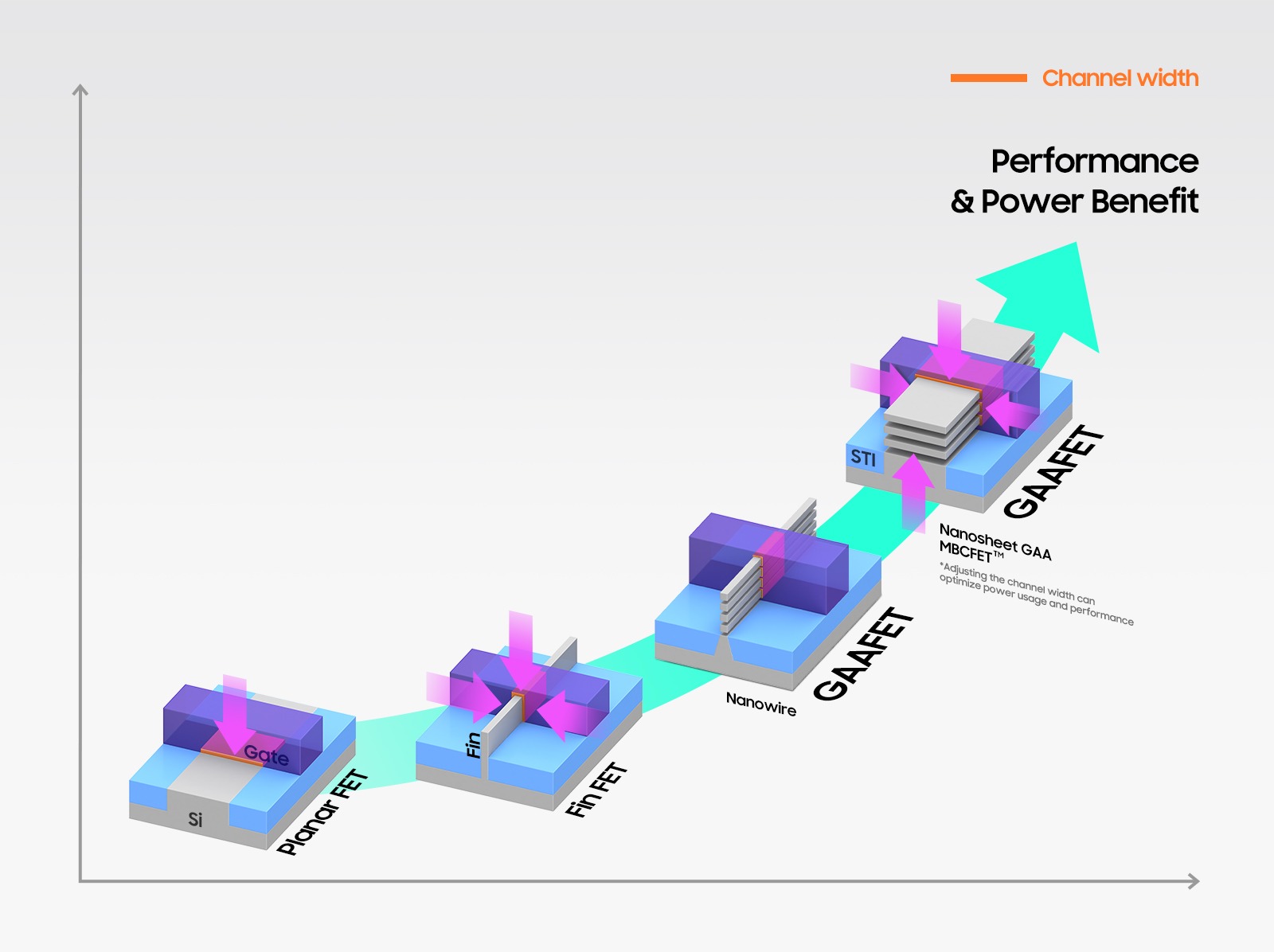

3nm Chips mat der MBCFET (Multi-Bridge-Channel) GAA Architektur wäerte méi héich Energieeffizienz gewannen, ënner anerem andeems d'Versuergungsspannung reduzéiert gëtt. Samsung benotzt och Nanoplat-Transistoren a Hallefleitchips fir High-Performance Smartphone Chipsets.

Am Verglach mat Nanowire Technologie, Nanoplacke mat méi breede Kanäl erlaben méi héich Leeschtung a besser Effizienz. Andeems Dir d'Breet vun den Nanoplacken upasst, kënnen Samsung Clienten d'Performance an d'Energieverbrauch un hir Besoinen upassen.

Dir kéint interesséiert sinn an

Am Verglach mat 5nm Chips, laut Samsung, hunn déi nei 23% méi héich Leeschtung, 45% manner Energieverbrauch an 16% méi kleng Fläch. Hir 2. Generatioun soll dann 30% besser Leeschtung, 50% méi Effizienz an eng 35% méi kleng Fläch bidden.

"Samsung wiisst séier wéi mir weider Leadership an der Uwendung vun nächster Generatioun Technologien an der Fabrikatioun weisen. Mir zielen dës Leedung mat dem éischten 3nm Prozess mat der MBCFETTM Architektur weiderzeféieren. Mir wäerte weider aktiv a kompetitiv Technologieentwécklungen innovéieren a Prozesser kreéieren déi hëllefen d'Erreeche vun der Technologie Reife ze beschleunegen. sot de Siyoung Choi, Chef vum Samsung Halbleitergeschäft.